# Section 7 Display/Terminal Management Processor (TMP)

From: ftp://bitsavers.informatik.uni-stuttgart.de/components/national/\_dataBooks/1988\_National\_Microcontrollers\_Databook.pdf

# **Section 7 Contents**

| ТМР                                                        | 7-3  |

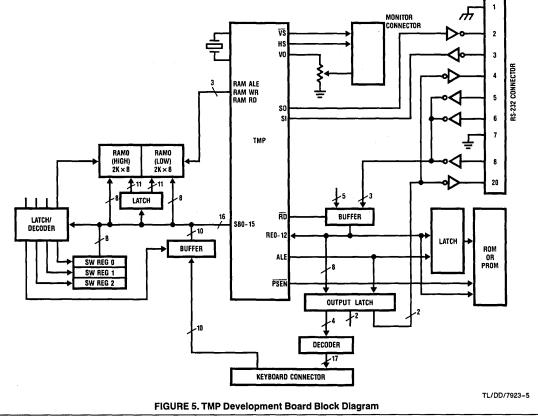

|------------------------------------------------------------|------|

| NS405 Series Display Terminal Management Processor (TMP)   | 7-4  |

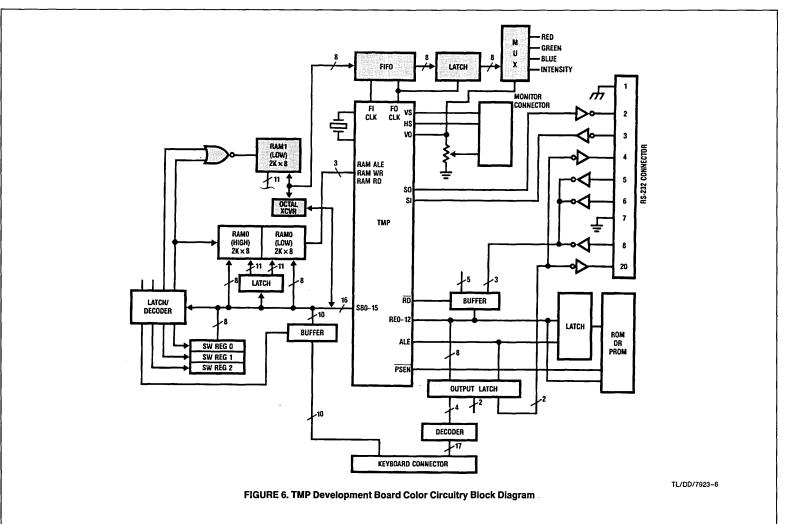

| AB-14 Throughput Considerations in NS405 System Planning   | 7-43 |

| AB-16 NS405-Series TMP External Interrupt Processing       | 7-44 |

| AN-354 TMP Row and Attribute Table Lookup Operation        | 7-46 |

| AN-355 TMP-Dynamic RAM Interfacing                         | 7-53 |

| AN-367 TMP External Character Generation                   | 7-58 |

| AN-369 NS405 TMP Logic Analyzer                            | 7-61 |

| AN-374 Building an Inexpensive But Powerful Color Terminal | 7-68 |

| AN-399 TMP Extended Program Memory                         | 7-73 |

# National Semiconductor

# **ТМР**ТМ

# **Terminal Management Processor**

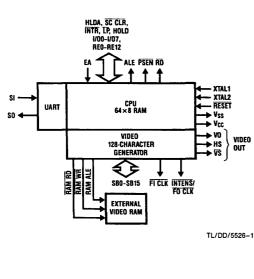

The TMP (NS405 series) is a single-chip CRT terminal display controller. The TMP is supported by the MOLE™ development system and replaces all the following LSI circuits commonly found in a terminal:

- Microprocessor

- Program ROM

- 64 x 8 RAM

- CRT controller

- DMA controller

- Character generator

- UART

- BAUD rate generator

- Parallel I/O controller

- Timer

The TMP offers complete CRT control over a wide scope of high-density circuit applications including phones, keyboard integration assignments, logic analyzers and more.

The NS455 Terminal Management Processor (TMP) demo board is available for design support.

Highly compact, the TMP board reduces previously necessary board space dramatically while providing 100% emulation of a classic low-end terminal. The board can also be used for TMP evaluation or as a vehicle for designing-in the NS405 device. INE

The board which is controlled by a preprogrammed NS455, needs only a video monitor, ASCII encoded keyboard, and power supply to provide your complete terminal. Should you wish to write your own program, no problem.

The cross-assembler software provides the capability. The board will execute custom programs through up to 8k of offchip memory.

The TMP demo board comes complete with operating manual, program source listing, board schematic, board layout, and all necessary connectors.

When you're ready to design your own TMP system, turn to National's MOLE development system. By using this system-comprised of brain board, personality board and software—you bring dedicated development support to the TMP chip, making design-in extremely fast and simple.

7-3

# PRELIMINARY

# National Semiconductor

# NS405-Series Display/Terminal Management **Processor (TMP)**

# **General Description**

The NS405 is a CRT terminal controller on a chip. It is a microcomputer system which replaces the following LSI circuits commonly found in a CRT data terminal:

- Microcomputer

- Baud Rate Generator

- CRT Controller

- Interrupt Controller Parallel I/O Controller

- DMA Controller

- Character Generator

- UART

In addition the NS405 includes powerful attribute logic, two

Timer

graphics display modes, and fast video output circuits.

The NS405 is primarily intended for use in low-cost terminals, but contains many features which make it a superior building block for "smart" terminals and word processing systems.

The NS405 interfaces easily to the display monitor, keyboard, display memory, and I/O ports. The architecture and instruction set are derived from the 8048-series microcontrollers. The instruction set has been enhanced and the architecture tailored to allow the NS405 CPU to efficiently manage a large display memory and an extensive interrupt environment.

The TMP can be used to easily and inexpensively add a display to many systems where it was previously impractical, it is not limited to terminal applications.

**Block and Connection Diagrams**

# Features

- Enhanced 8048 instruction set and architecture

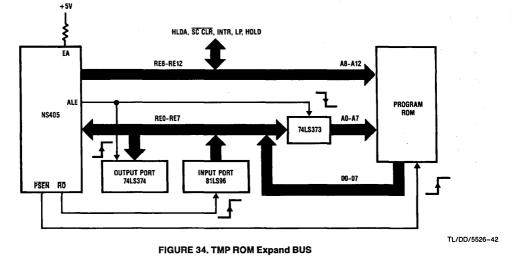

- Up to 8k x 8 ROM external with ROM expand bus

- On-board RAM 64 x 8

- Programmable display format

- On-board video memory management unit

- 16-bit bidirectional display memory bus (direct video and attribute RAM interface)

- Built-in timer

- Real-time clock (may be programmed for 1 Hz)

- Video control signals

- Eight independent attributes

- Pixel and block graphics display modes

- Programmable cursor characteristics

- Programmable CRT refresh rate

- Light pen feature

- UART, programmable baud rate up to 19.2k baud

- Character generator (128 characters 7 x 11 max)

- Single 5-volt supply @ 110 mA (typ)

- Up to 18 MHz video dot rate (12 MHz CPU clock)

- 48-pin package

- 8-bit parallel I/O port (multiplexed with external ROM)

- Extensive I/O expansion capabilities

- Up to 64k by 8 or 16 video RAM

7-4

# Absolute Maximum Ratings

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Temperature Under Bias            | 0°C to +70°C    |

|-----------------------------------|-----------------|

| Storage Temperature               | -65°C to +150°C |

| All Input or Output Voltages      |                 |

| with Respect to V <sub>SS</sub> * | -0.5V to +7.0V  |

# Power Dissipation ESD

\*EA, SI and VSYNC may be subjected to V<sub>SS</sub> + 15V.

Note: Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended; operations should be limited to those conditions specified under DC Electrical Characteristics.

# **DC Electrical Characteristics**

$T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{CC} = +5V \pm 10^{\circ}$ ,  $V_{SS} = 0V$ , unless otherwise specified

| Symbol           | Parameter                                                        | Test Conditions                       | Min  | Max             | Units |

|------------------|------------------------------------------------------------------|---------------------------------------|------|-----------------|-------|

| V <sub>IL1</sub> | Input Low Voltage (All Except XTAL1, XTAL2, RESET)               |                                       | -0.5 | 0.8             | V     |

| V <sub>IH1</sub> | Input High Voltage (All Except XTAL1, XTAL2, RESET)              |                                       | 2.0  | V <sub>CC</sub> | V     |

| VIL2             | Input Low Voltage (XTAL1, XTAL2, RESET)                          |                                       | -0.5 | 0.6             | V     |

| V <sub>IH2</sub> | Input High Voltage (XTAL1, XTAL2, RESET)                         |                                       | 3.8  | Vcc             | V     |

| VOL              | Output Low Voltage (All Except INTENS, VO)                       | I <sub>OL</sub> = 2.0 mA              |      | 0.4             | V     |

| V <sub>OH</sub>  | Output High Voltage (All Except INTENS, VO)                      | I <sub>OH</sub> =125 μA               | 2.4  | Vcc             | v     |

| VOL              | Output Low Voltage (INTENS, VO)                                  | I <sub>OL</sub> = 5.0 mA              |      | 0.4             | V     |

| V <sub>OH</sub>  | Output High Voltage (INTENS, VO)                                 | I <sub>OH</sub> = −500 μA             | 2.4  |                 | V     |

| l <sub>IL</sub>  | Input Leakage Current (EA, INT, SI)                              | $V_{SS} \le V_{IN} \le V_{CC}$        |      | ±10             | μΑ    |

| lol              | Output Leakage Current<br>(ROM Expand Bus, High Impedance State) | $V_{CC} \ge V_{IN} \ge V_{SS} + 0.45$ |      | ±10             | μΑ    |

| lol              | Output Leakage Current<br>(System Bus, High Impedance State)     | $V_{CC} \ge V_{IN} \ge V_{SS} + 0.45$ |      | ±100            | μΑ    |

| Icc              | Total Supply Current                                             | T <sub>A</sub> = 25°C                 |      | 150             | mA    |

# **AC Electrical Characteristics**

$T_A = 0^{\circ}C$  to +70°C,  $V_{CC} = +5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise specified

| Symbol                      | Parameter                                             | Min  | Max   | Units |  |  |

|-----------------------------|-------------------------------------------------------|------|-------|-------|--|--|

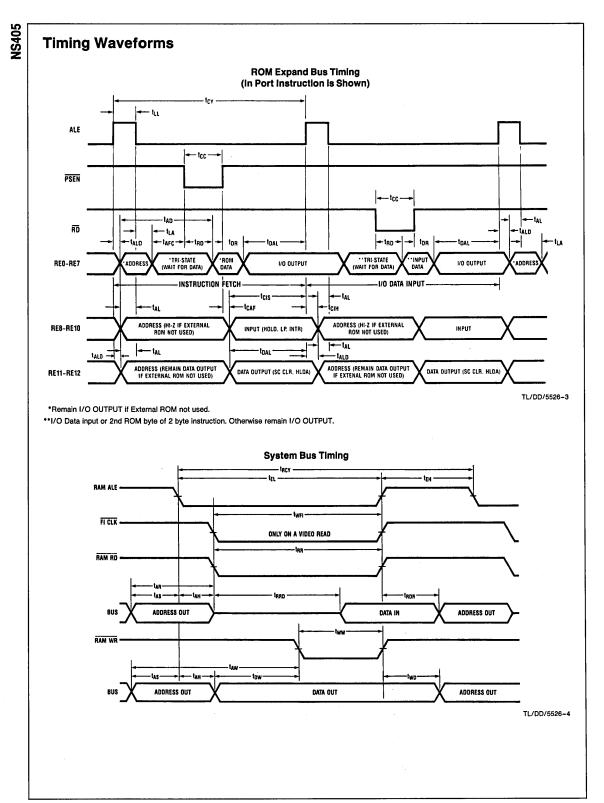

| I AND ROM EXPAND BUS TIMING |                                                       |      |       |       |  |  |

| F <sub>XTAL</sub>           | Crystal Frequency                                     | 3    | 18    | MHz   |  |  |

| FCPU                        | CPU Frequency                                         | 3    | 12    | MHz   |  |  |

| t <sub>CY</sub>             | CPU Cycle Time                                        | 1.25 | 7.5   | μs    |  |  |

| t <sub>DF</sub>             | Video Dot Time                                        | 55.5 | 333.3 | ns    |  |  |

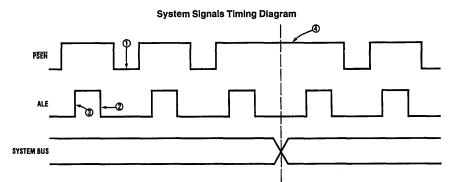

| tLL                         | ALE Pulse Width (Note 1)                              | 125  |       | ns    |  |  |

| t <sub>AL</sub>             | Address Setup to ALE (Note 1)                         | 55   |       | ns    |  |  |

| t <sub>LA</sub>             | Address Hold from ALE (Note 1)                        | 40   |       | ns    |  |  |

| t <sub>CC</sub>             | Control Pulse Width PSEN, RD (Note 1)                 | 250  |       | ns    |  |  |

| t <sub>DR</sub>             | Data Hold (Notes 1, 4)                                | 0    | 100   | ns    |  |  |

| t <sub>RD</sub>             | PSEN, RD to Data In (Note 1)                          |      | 220   | ns    |  |  |

| t <sub>AD</sub>             | Address Setup to Data In (Note 1)                     |      | 360   | ns    |  |  |

| tAFC                        | Address Float to RD, PSEN (Notes 1, 5)                | 0    |       | ns    |  |  |

| t <sub>CAF</sub>            | PSEN to Address Float (Notes 1, 5)                    | -10  | + 10  | ns    |  |  |

| t <sub>DAL</sub>            | Data Setup to ALE (RE0-7, 11, 12) (Note 1)            | 55   |       | ns    |  |  |

| t <sub>ALD</sub>            | Data Hold from ALE (RE0-7, 11, 12) (Note 1)           | 40   |       | ns    |  |  |

| t <sub>CIS</sub>            | Control Input Setup to ALE (RE8, 9, 10) (Note 1)      | 240  |       | ns    |  |  |

| t <sub>CIH</sub>            | Control Input Hold from ALE (RE8, 9, 10) (Notes 1, 4) | 75   | 125   | ns    |  |  |

NS405

1.5W

2000V

# **AC Electrical Characteristics**

$T_A$  = 0°C to +70°C,  $V_{CC}$  = +5V ±10%,  $V_{SS}$  = 0V, unless otherwise specified (Continued)

| Symbol           | Parameter                                  | Min                               | Max | Units |

|------------------|--------------------------------------------|-----------------------------------|-----|-------|

| TEM BUS TIMIN    | G                                          | · · · · · ·                       |     |       |

| t <sub>EL</sub>  | RAM ALE Low Time (Note 1)                  | 250                               |     | ns    |

| t <sub>EH</sub>  | RAM ALE High Time (Note 1)                 | 100                               |     | ns    |

| tAS              | Address Setup to RAM ALE (Note 1)          | 20                                |     | ns    |

| t <sub>AH</sub>  | Address Hold from RAM ALE (Note 1)         | 10                                |     | ns    |

| t <sub>RR</sub>  | RAM RD Width (Note 1)                      | 210                               |     | ns    |

| t <sub>AR</sub>  | Address Setup to RAM RD (Note 1)           | 80                                |     | ns    |

| tRRD             | Data Access from RAM RD (Note 1)           |                                   | 140 | ns    |

| tRDR             | Data Hold from RAM RD (Notes 1, 4)         | 0 60                              |     | ns    |

| t <sub>WFI</sub> | FIFO In Clock Width (Note 1)               | 210                               |     | ns    |

| tww              | RAM WR Strobe Width (Note 1)               | 130                               |     | ns    |

| t <sub>AW</sub>  | Address Setup to RAM WR (Note 1)           | 120                               |     | ns    |

| t <sub>DW</sub>  | Data Setup to RAM WR (Note 1)              | 10                                |     | ns    |

| t <sub>WD</sub>  | Data Hold from RAM WR (Note 1)             | Data Hold from RAM WR (Note 1) 20 |     |       |

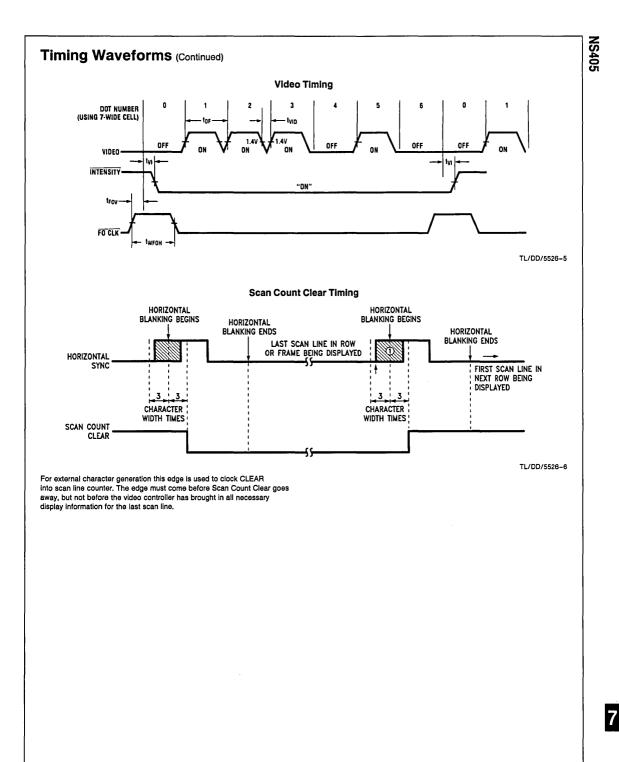

| EO TIMING        |                                            |                                   |     |       |

| t <sub>DF</sub>  | Dot Period = $\frac{1}{f_c}$ (Note 1)      | 55                                |     | ns    |

| t <sub>VID</sub> | Video Blank Time (Note 1)                  | 5                                 | 15  | ns    |

| t <sub>VI</sub>  | Skew, Intensity to Dot 0 (Note 1)          | - 15                              | 15  | ns    |

| tFOV             | FIFO Out Clock to Dot 0 (Note 1)           | 15                                |     |       |

| twFOH            | FIFO Out Clock Width High (Note 1, Note 2) | 55                                | 165 | ns    |

\*1/3 CPU cycle.

\*\*1 Dot time is 55 ns.

Note 1: Control outputs  $C_L = 80 \text{ pF}$ ; ROM Expand Bus outputs  $C_L = 150 \text{ pF}$ ; System Bus outputs  $C_L = 100 \text{ pF}$ ;  $V_{OUT}$  & INTENS outputs  $C_L \approx 50 \text{ pF}$ ;  $F_{XTAL} = 18 \text{ MHz}$ ;  $F_{CPU} = 12 \text{ MHz}$ . XTAL1 & XTAL2 driven externally per *Figure 12b* with 50% duty cycle.

Note 2: FO CLK duty cycle is shown above.

Note 3: Hold request is latched. It is honored at the start of the next vertical retrace.

Note 4: Max spec. listed for user information only, to prevent bus contention. Maximum value not tested.

Note 5: Not tested.

| Character<br>Cell Width | FIFO Out<br>HIGH | FIFO Out<br>LOW |  |  |

|-------------------------|------------------|-----------------|--|--|

| 6                       | 1 dot            | 5 dots          |  |  |

| 7                       | 2 dots           | 5 dots          |  |  |

| 8                       | 2 dots           | 6 dots          |  |  |

| 9                       | 3 dots           | 6 dots          |  |  |

| 10                      | 3 dots           | 7 dots          |  |  |

# **Input Hold Times**

$T_A = 25^{\circ}C, V_{CC} = +5V \pm 10\%, V_{SS} = 0V$

| Input              | Min Active Time                                   |

|--------------------|---------------------------------------------------|

| Reset              | 50 ms (power up)<br>5 CPU Cycles (after power up) |

| External Interrupt | 2 CPU Cycle                                       |

| Light Pen          | 1 CPU Cycle                                       |

| I/O Input          | 1 CPU Cycle                                       |

| Hold Request       | 1 CPU Cycle (Note 3)                              |

# FIFO

Fall through should not be greater than 4 character times (character time =  $1/f_{XTAL} \times #dots/cell$ ).

Throughput rate must be at least the character rate (character rate = 1/character time).

| Symbol           | Parameter         | Test Conditions |                            |                                                                               | Min                                      | Max | Units   |

|------------------|-------------------|-----------------|----------------------------|-------------------------------------------------------------------------------|------------------------------------------|-----|---------|

| CIN              | Input Capacitance | Fc ≕            | 1 MHz (Note 5)             |                                                                               |                                          | 10  | pF      |

| С <sub>ОИТ</sub> | Output and Reset  | Unme            | asured Pins Returned       | to V <sub>SS</sub> (Note 5)                                                   |                                          | 20  | pF      |

|                  | trical Characteri |                 | -                          | Time                                                                          |                                          |     |         |

| Symbol           |                   | Paramete        | er                         |                                                                               | Тур                                      |     |         |

| t <sub>LL</sub>  | ALE Pulse Wi      | dth             |                            |                                                                               | 14 t <sub>CY</sub>                       | /60 |         |

| t <sub>AL</sub>  | Address Setu      | p to ALE        |                            |                                                                               | 8 t <sub>CY/</sub>                       | 60  |         |

| t <sub>LA</sub>  | Address Hold      | from ALE        |                            |                                                                               | 6 t <sub>CY/</sub>                       | 60  |         |

| tcc              | Control Pulse     | Width           | PSEN<br>RD                 | 24 t <sub>CY/60</sub><br>36 t <sub>CY/60</sub>                                |                                          |     |         |

| tCY              | CPU Cycle Ti      | me              |                            | $60 t_{CY/60} = 15/f_{CPU} = \frac{15}{f_{XTAL} \div 1 \text{ or } \div 1.5}$ |                                          |     | r ÷ 1.5 |

| t <sub>DR</sub>  | Data Hold         |                 | ······                     | -2 t <sub>CY/60</sub>                                                         |                                          |     |         |

| t <sub>RD</sub>  | Control Pulse     | to Data li      | n PSEN<br>RD               | 18 t <sub>CY/60</sub><br>30 t <sub>CY/60</sub>                                |                                          |     |         |

| t <sub>AD</sub>  | Address Setu      | p to Data       | In                         |                                                                               | 32 t <sub>CY</sub> ,                     | /60 |         |

| t <sub>AFC</sub> | Address Floa      | t to            | PSEN<br>RD                 |                                                                               | 2 t <sub>CY/</sub><br>2 t <sub>CY/</sub> |     |         |

| tCAF             | PSEN to Add       | ress Float      |                            |                                                                               | 0 t <sub>CY/</sub>                       | 60  |         |

| t <sub>DAL</sub> | Data Setup to     | ALE             | RE0–7<br>RE8–10<br>RE11–12 | 6 t <sub>CY/60</sub><br>-2 t <sub>CY/60</sub><br>16 t <sub>CY/60</sub>        |                                          |     |         |

| t <sub>ALD</sub> | Data Hold fro     | m ALE           | RE0-7<br>RE8-12            | 2 t <sub>CY/60</sub><br>6 t <sub>CY/60</sub>                                  |                                          |     |         |

#### Ticks Symbol Parameter Min Max RAM ALE Low Time 14 t<sub>CY/60</sub> - 42 ns t<sub>EL</sub> t<sub>EH</sub> RAM ALE High Time 6 t<sub>CY/60</sub> - 25 ns t<sub>AS</sub> Address Setup to RAM ALE 4 t<sub>CY/60</sub> - 60 ns Address Hold from RAM ALE 2 t<sub>CY/60</sub> - 40 ns t<sub>AH</sub> Read or Write Cycle Time **t**RCY RAM RD Width t<sub>RR</sub> 12 t<sub>CY/60</sub> - 40 ns Address Setup to RAM RD 6 t<sub>CY/60</sub> - 45 ns t<sub>AR</sub> Data Access from RAM RD $10 t_{CY/60} - 70 \text{ ns}$ tRRD Data Hold from RAM RD t<sub>RDR</sub> FIFO In Clock Width 12 t<sub>CY/60</sub> - 40 ns t<sub>WFI</sub> RAM WR Strobe Width 8 t<sub>CY/60</sub> - 27 ns tww Address Setup to RAM WR 10 t<sub>CY/60</sub> - 90 ns t<sub>AW</sub> t<sub>DW</sub> Data Setup to RAM WR 2 t<sub>CY/60</sub> - 30 ns Data Hold from RAM WR 2 t<sub>CY/60</sub> - 20 ns twp

NS405

7

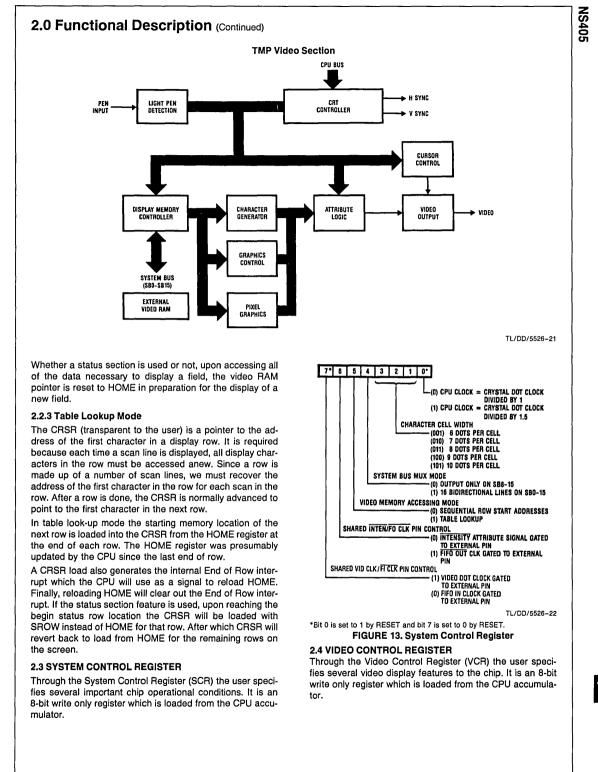

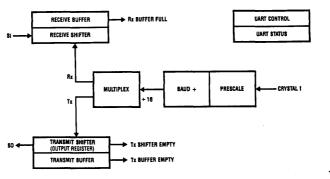

NS405-Series Detailed RE12 RE11 RE10 RE9 RE8 XTAL1 XTAL2 HLDA SC CLR INTR LP HOLD EA 23 22 25 36 **I**37 38 39 29 ٦. - 6 SI RECEIVE REG. UART CONTROL INTERRUPT REG. ← TIMER ← ÷32 ← ÷15 ← r)I CLOCK ROM EXPAND OUT 40 RED, 1/00 34 ROM RECEIVE BUF. REGISTERS اجا GENERATOR INTERBUPT MASK MUX CNTL INPUT - PSEN CPU CLK 🗲 41 RE1. 1/01 EXPAND ΪP 2×8 INTERRUPT 42 RE2. 1/02 GEN'L. CONTROL 5 BAUD RATE 43 RE3, 1/03 L DOT INTR 1/0 CONTROL REGS PROGRAM COUNTER CLOCK PORT 🕈 RE4, 1/04 2×8 -8 13 BITS 44 STACK 45 RE5, 1/05 REAL ALĚ 🗕 POINTER MUX XMIT BUFFER UART TIME PSEN-+ CNTL. RAM 43 RE6, 1/06 46 RE7, 1/07 S0 **∢**33 STATUS REG. XMIT REG. INTERRUPT 64×8 8D-UART AND BAUD RATE ALU GENERATOR ALE 📣 21 FO CLK HIGH RAM ALE **18** ACCUMULATOR TIMING ACCUMULATOR , RAM WR SIGNAL EA DOT CLK 19 GENERATION RAM RD CPU CLK 20 FI CLK 17 PSEN **4**<u>30</u>⊧ RD 431 I <sub>VERT</sub> CHARACTER DISPLAY MEMORY ATTRIBUTE HORIZONTAL HORIZONTAL EOR GENERATOR LATCHES **CONTROL REGISTERS I** CONTROL SYNC CHARACTER CONTROL 7×11×128 ROM 7×16 2×8 REGISTERS → HS 28 DOT REGISTERS **4 CHARACTER** SYNC, BLANK, DISPLAY MEMORY ATTRIBUTE CLK LENGTH FIFO **CONTROL REGISTERS II** GRAPHICS LOGIC **17 BITS** 3×8 GENERATOR SCAN FO CLK VERTICAL VERTICAL CONTROL CONTROL 8 DATA SYNC **DISPLAY MEMORY** REGISTERS INTENSITY REGISTERS **8 ATTRIBUTES** CONTROL **VIDEO CONTROL** 27 VS DISPLAY SELECT 1 CURSOR REGISTER SELECT SYNC. BLANK. BLINK SELECT LOGIC LENGTH REGISTER SYSTEM CONTROL CONTROL REGISTER **CRT REFRESH AND** VIDEO CONTROL CONTROL LOGIC LOGIC/OUTPUT

26

**VIDEO OUTPUT**

(VO)

25

INTENS/

FO CLK

4 48

Vcc

**Block Diagram**

NS405

1-16

SB0-SB15

TL/DD/5526-7

REAL TIME INTERRUPT

**4** 32

RESET

**4** 24

Vss

# 1.0 Functional Pin Descriptions

| 1.1 SUP      | PLIES                                                  |                                                                                                                                                                                                                                                                                                                                                                |

|--------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin          | Name                                                   | Function                                                                                                                                                                                                                                                                                                                                                       |

| 48           | V <sub>CC</sub> — Power                                | 5V ±10%                                                                                                                                                                                                                                                                                                                                                        |

| 24           | V <sub>SS</sub> — Ground Reference                     |                                                                                                                                                                                                                                                                                                                                                                |

|              | JT SIGNALS                                             |                                                                                                                                                                                                                                                                                                                                                                |

| 23, 22<br>29 | XTAL1, XTAL2 — Crystal 1, 2:<br>EA — External Access:  | Crystal connections for clock oscillator (3–18 MHz).<br>Pull HIGH (V <sub>IH2</sub> )                                                                                                                                                                                                                                                                          |

| 32           | RESET                                                  | An active low input that initializes the processor. The RESET input is also used for internal ROM verification.                                                                                                                                                                                                                                                |

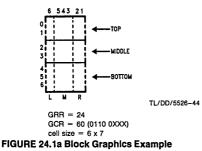

| 34           | SI — Serial Input:                                     | Drives receiver section of UART (true data).                                                                                                                                                                                                                                                                                                                   |

|              | PUT SIGNALS                                            |                                                                                                                                                                                                                                                                                                                                                                |

| 33           | SO — Serial Output:                                    | Driven by transmitter section of UART (true data).                                                                                                                                                                                                                                                                                                             |

| 21           | ALE — Address Latch Enable:                            | ROM address is available on the ROM Expand Bus and may be latched<br>on the falling edge of ALE. Port output data may be latched on the rising<br>edge of ALE. ALE pulses are always present, even if EA is tied low.                                                                                                                                          |

| 30           | PSEN — Program Store Enable:                           | Enable external ROM output drivers when low. <u>PSEN</u> is idle (high) when the CPU fetches from internal ROM.                                                                                                                                                                                                                                                |

| 31           | RD — Read Port Data:                                   | Accept Port input data on ROM Expand Bus RE0–RE7 while low. ROM<br>Expand Bus is in high impedance state while RD is low.                                                                                                                                                                                                                                      |

| 28           | HS — Horizontal Sync                                   | The rising edge of HS is controlled by the Horizontal Sync Begin Register<br>and the falling edge is controlled by the Horizontal Sync End Register. HS<br>is disabled (low) if bit 5 of the Video Control Register $= 0$ .                                                                                                                                    |

| 27           | VS — Vertical Sync Output:                             | The falling edge of $\overline{VS}$ is controlled by the Vertical Sync Begin Register<br>and the rising edge is controlled by the Vertical Sync End Register. $\overline{VS}$ is<br>at TRI-STATE if bit 5 of the Video Control Register = 0.                                                                                                                   |

| 26           | VO — Video Output:                                     | High = beam on, low = beam off. VO is disabled (low) if bit 5 of the<br>Video Control Register = 0.                                                                                                                                                                                                                                                            |

| 25           | INTENS/FO CLK                                          | (Shared pin) INTENS Signal under attribute control may be used to switch<br>the bistable brightness of display characters.<br>FIFO Out Clock may be used to clock data from an external FIFO in<br>synchronism with data from the internal FIFO.                                                                                                               |

| 17           | VID CLK/FI CLK — Video Dot Clock Out/<br>FIFO IN CLOCK | Both CANNOT be used simultaneously.<br>(Shared pin) The rising edge of the Video Dot Clock may be used to clock<br>the data out of the video output pin. FIFO In Clock may be used to clock<br>data from an extended attribute RAM into an external FIFO in<br>synchronism with the data loaded into the internal FIFO.<br>Both CANNOT be used simultaneously. |

| 18           | RAM ALE — RAM Address Latch Enable:                    | RAM address is available on the System Bus and may be latched on the<br>falling edge of RAM ALE. Only operational when Display RAM accesses<br>being performed. Otherwise high.                                                                                                                                                                                |

| 20           | RAM RD RAM Read:                                       | Enable display RAM data onto the System Bus when RAM RD is low.                                                                                                                                                                                                                                                                                                |

| 19           | RAM WR — RAM Write:                                    | Data to RAM is available on the System Bus and may be written at the                                                                                                                                                                                                                                                                                           |

|              |                                                        | rising edge of RAM WR.                                                                                                                                                                                                                                                                                                                                         |

| 1.4 BUS      |                                                        |                                                                                                                                                                                                                                                                                                                                                                |

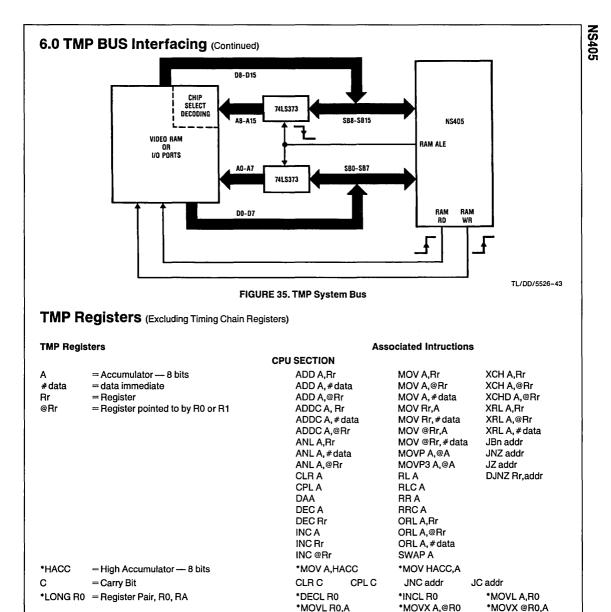

| 1–8          | SB0-SB7 — System Bus 0-7:                              | Display RAM address is output while RAM ALE is high and may be<br>latched on the falling edge of RAM ALE. System Bus accepts data input<br>while RAM RD is low and outputs data while RAM WR is low.                                                                                                                                                           |

| 9–16         | SB8-SB15 — System Bus 8-15:                            | Normally, Display RAM address is output and held on these pins for the full read or write cycle. However, if bit 4 of the System Control Register is set, these pins function bidirectionally like SB0–SB7 to allow 16-bit data words for attribute operation.                                                                                                 |

| 35–47        | RE0-12 — ROM Expand Bus 0-12:                          | Used for program ROM expansion as described below. Time multiplexed with I/O port and system control signals. I/O port and system control signals only if no external ROM used.                                                                                                                                                                                |

| 40–47        | RE0-RE7                                                | Low order ROM address is output and may be latched on the falling edge of ALE. Enable ROM data to this Bus when $\overrightarrow{\text{PSEN}}$ is low. Enable I/O port input data to the Bus when $\overrightarrow{\text{RD}}$ is low. Use the rising edge of ALE to latch port output data.                                                                   |

| 1.0 Fu | 1.0 Functional Pin Description (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|--------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin    | Name                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

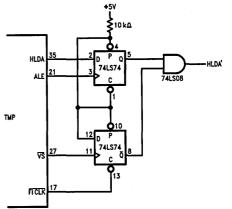

| 39–35  | RE8-RE12                                   | Five most significant bits of the ROM address are output during ALE and remain stable until data is read in during PSEN. These pins are multiplexed with the HLDA, INTR, IP, SC CLR, and HOLD signals.                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 37     | INTR — Interrupt: RE10                     | An active low input that interrupts the processor if the external interrupt is<br>enabled. Because it shares a pin with RE10, INTR may be driven directly<br>only if no external ROM is used (EA is low). Otherwise must be driven<br>through a 3.9k resistor.*                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 38     | IP — Light Pen Interrupt: RE9              | An active low input that interrupts the processor if internal interrupts are<br>enabled and bit 5 in the Interrupt Mask Register is set. Because it shares<br>a pin with RE9, LP may be driven directly only if EA is low. Otherwise,<br>must be driven through a 3.9k resistor.*                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 39     | HOLD — HOLD request: RE8                   | When high, requests that the NS405 enter the Hold mode. When in the<br>Hold mode the System Bus will be in a high impedance state. The Hold<br>mode is granted at the beginning of the next vertical retrace. Because it<br>shares a pin with RE8, HOLD may be driven directly only if EA is low.<br>Otherwise, must be driven through a 3.9k resistor.*                                                                                                               |  |  |  |  |  |  |  |

| 35     | HLDA — Hold Acknowledge: RE12              | This output is asserted in response to Hold and provides handshake capability with another processor (active high). For more detailed information see Section 3.0 Slave Processing. Because HLDA shares a pin with RE12, the HLDA state is preset only during the interval preceding the rising edge of ALE. However, if no external ROM is used, HLDA is a steady state output and need not be latched externally.                                                    |  |  |  |  |  |  |  |

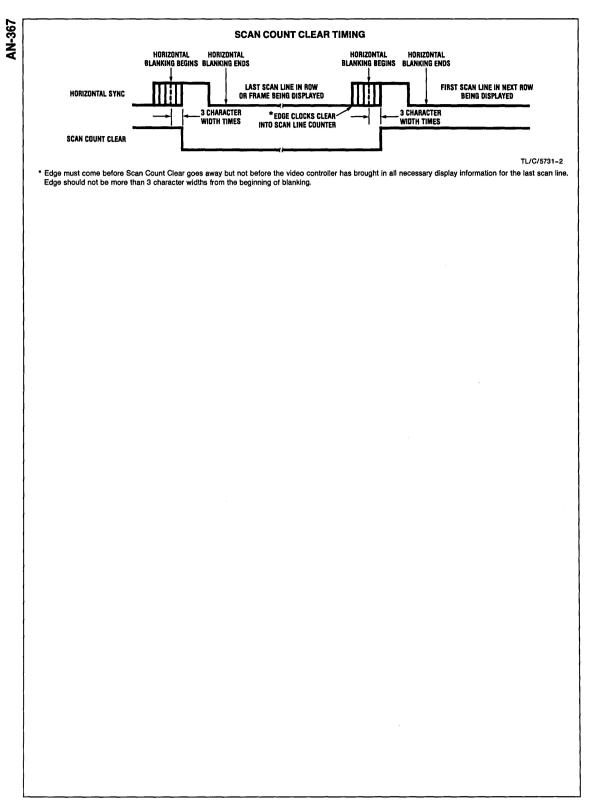

| 36     | SC CLR — Scan Count Clear: RE11            | This output clears an external scan counter when used with an external character generator. It is a low going pulse which occurs during the horizontal retrace preceding the first scan line of each character row. Because SC CLR shares a pin with the RE11, the correct SC CLR state is present only during the interval preceding the rising edge of ALE. However, if no external ROM is used, SC CLR is a steady state output and need not be latched externally. |  |  |  |  |  |  |  |

\*Unused control inputs must be terminated

**NS405**

# 2.0 Functional Description 2.1 CPU

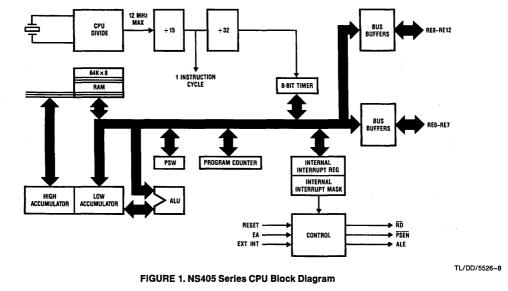

The CPU of the NS405 is patterned after the 8048 single chip microcomputer (see *Figure 1*).

7-12

# 2.1.1 Accumulator — High Accumulator

In addition to the regular 8-bit Accumulator, there is an 8-bit High Accumulator extension to facilitate the 16-bit operations required for display memory management. The HACC/ ACC pair is usually used in conjunction with the 16-bit RAM pointer registers (RA, R0 and RB, R1, CURSOR, HOME, BEGD and ENDD) to effect video data transfers. In addition, external attribute memory is loaded in a 16-bit transfer operation. Any instruction which causes a carry or borrow out of the low accumulator will affect the high accumulator (see *Figure 2*).

Auxiliary carry is used only when converting the accumulator contents from binary to BCD (binary coded decimal) using the DA A instruction. The auxiliary carry flag can be cleared by moving a zero into bit 6 of the program status word.

**FIGURE 2. CPU Accumulator**

# 2.1.2 Program Counter (PC)

The Program Counter is a 13-bit wide register which provides program addressing for the CPU. The lower 11 bits operate like a conventional program counter while the upper 2 bits are actually latches. These 2 latches are automatically loaded from the bank select flip-flops (PSW bits 3, 4) whenever a JMP or CALL instruction is executed. The bank select flip-flops in turn are only modified upon the execution of a Select Memory Bank Instruction or modification of the PSW (see *Figure 3*).

BANK SELECT BITS (LATCHES) (LOADED BY EXECUTION OF JMP OR CALL)

TL/DD/5526-10

#### FIGURE 3. TMP Program Counter

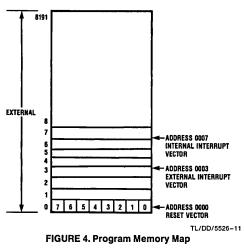

#### 2.1.3 Program Memory

Memory is subdivided into 2k banks with accesses limited to the currently selected bank unless a Bank Change sequence has been executed. Upon reaching the end of a memory bank, the program counter will wrap around and point to the beginning of the current bank.

Each bank is further subdivided into pages of 256 bytes each, with 8 pages in every bank. The conditional JUMP instructions are restricted to operate within the memory page that they reside in.

Because of the sequence which the CALL instruction executes when pushing and loading the PC, it is possible to easily call and return from subroutines located in different memory banks (see *Figure 4*).

Upon executing an RET or RETR instruction for a call from one memory bank into another, a SEL MBx instruction should be excuted to restore the memory bank select flipflops to their original bank. However, no SEL MBx is needed after an interrupt since the flip-flops were never modified.

2.1.4 Program Status Word Bit Assignments

| Bit<br>Position | Contents                                     |

|-----------------|----------------------------------------------|

| 0               | Stack Pointer Bit, S0                        |

| 1               | Stack Pointer Bit, S1                        |

| 2               | Stack Pointer Bit, S2                        |

| 3*              | Memory Bank Select Bit 0                     |

| 4*              | Memory Bank Select Bit 1                     |

| 5*              | Register Bank Select Bit (0 = Bank 0,        |

|                 | 1 = Bank 1)                                  |

| 6*              | Auxiliary Carry. A carry from Bit 3 to Bit 4 |

|                 | generated by an add operation. Used only by  |

|                 | the decimal adjust (DA A) instruction.       |

| 7*              | Carry. A bit indicating the preceding        |

|                 | operation resulted in an overflow or an      |

|                 | underflow from the 8-bit accumulator.        |

\*Note 1: Bits 3 through 7 are saved on the stack by subroutine calls or interrupts. Bits 3 and 4 are restored upon execution of an RET instruction, whereas all 5 bits are restored by RETR.

Note 2: F0 is not saved on the stack (as in an 8048).

Note 3: Bits 0-5 cleared on a RESET.

#### 2.1.5 Stack Pointer (SP)

The stack pointer is an independent 3-bit counter which points to designated locations in the internal RAM that holds subroutine return parameters. The stack itself is located in RAM locations 8-23 (see *Figure 5*).

Each entry in the stack takes up two bytes and contains both the PC and status bits. When reset to zero, the stack pointer actually points to locations 8 and 9 in RAM. Since the stack pointer is a simple up/down counter, an overflow will cause the deepest stack entry to be lost (the counter overflows from 111 to 000 and underflows from 000 to 111). Note: If the level of subroutine nesting is less than eight (8), the unneeded

stack locations may be used as RAM.

|     |                 |     |   |            |   |   | LOCATION | POINTER       |

|-----|-----------------|-----|---|------------|---|---|----------|---------------|

| F   | PSW3-7<br>PC4-7 |     |   | 3-7 PC8-12 |   |   | 9        | 000           |

|     |                 |     |   | PC0-3      |   |   | 1.       | 000           |

| 9 8 | 7 6 1           | 5 4 | 3 | 2          | 1 | 0 | Γ        | TL/DD/5526-12 |

Note: The odd numbered RAM bytes in the stack area have two (2) extra bits to allow for storage of the bank select switch bits. This feature allows interrupt routines and subroutines to be located outside the current 2k program memory bank.

FIGURE 5. Typical Stack Composition

# 2.0 Functional Description (Continued)

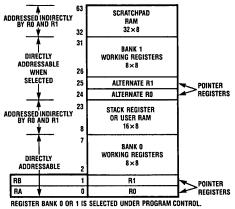

## 2.1.6 Data Memory (On-Chip RAM)

The data memory nominally consists of 64 8-bit locations and is utilized for working registers, the subroutine stack, pointer registers and scratch pad. There are two sets of working/pointer registers (R0–R7) which are selected by the Select RAM Bank instruction. The stack area is located in locations 8–23. Locations 32–63 contain the scratch pad memory. To facilitate 16-bit Video Memory Management there are two 8-bit extension registers (RA and RB) which are associated with the R0 and R1 registers respectively of whichever RAM bank is currently selected (see *Figure 6*). i.e., There is only one RA register and only one RB register.

TL/DD/5526-13

#### FIGURE 6. RAM Memory Map

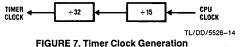

#### 2.1.7 Timer

The On-Board Timer is an 8-bit up counter which sets the Timer Overflow Flag and generates an internal interrupt (if enabled) whenever it overflows from FF to zero. The Timer may be stopped, started, loaded and read from by the CPU. The Timer clock is derived from the CPU clock as shown in *Figure 7*. Whenever a Start Timer instruction is executed the  $\div$  32 is initialized to its zero state to insure a full count measurement. After overflow the timer keeps counting until the next FF to zero overflow at which time the overflow flag will be set and another interrupt generated. The overflow flag can only be reset through the JTF and JNTF instructions.

# 2.1.8 Interrupts

The interrupt circuitry handles two generic classes of interrupt conditions called Internal and External. Either class has its own master control which can be activated through software enable and disable instructions. On an interrupt service the currently executing instruction is completed, then two CPU cycles are used as the program counter and bits 3–7 of the PSW are pushed onto the stack and stack pointer is incremented. Then the interrupt vector address (3 or 7) is loaded into the PC and service started. Whenever an interrupt condition is being serviced all other interrupts of either class are locked out until a RETR instruction is executed to conclude interrupt service. If both an external and internal interrupt arrive at the same time, the external interrupt is recognized first.

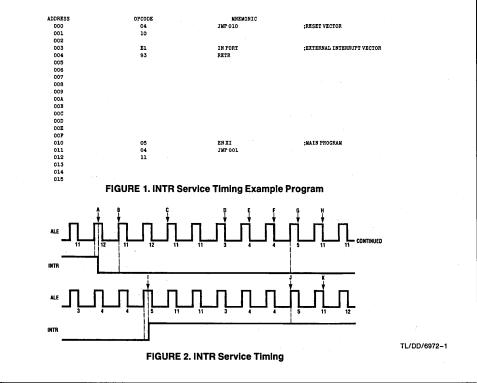

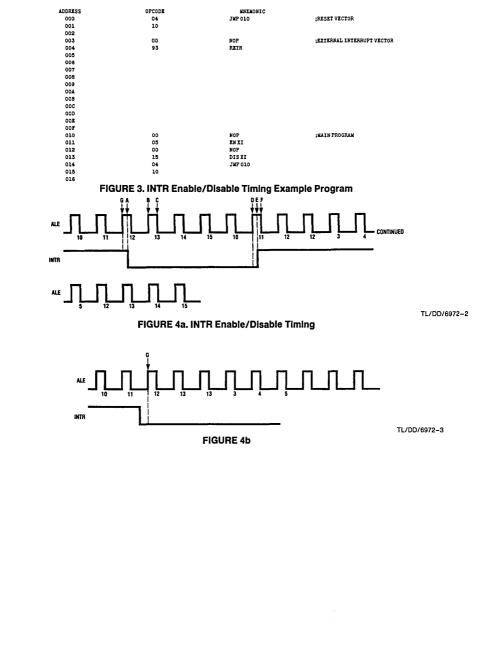

#### 2.1.8.1 External Interrupt

The External Interrupt consists solely of the shared INTR/ RE10 pin. External interrupts on this pin will be detected if the setup and hold times as shown in the timing diagrams are met. This pin is a level sampled interrupt which means that as long as the pin is low during the sampling window an interrupt will be generated. In addition, the INTR pin is the only external pin whose logic state can be directly tested through software.

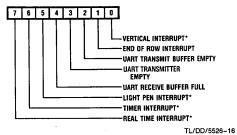

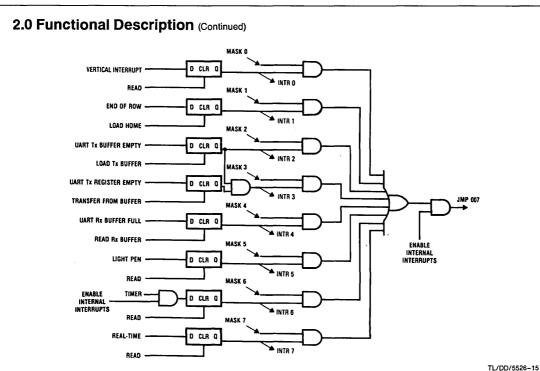

#### 2.1.8.2 Internal Interrupts

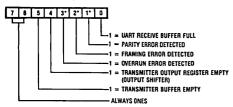

The Internal Interrupts consist of seven internal operational conditions plus the light pen arranged in an 8-bit wide register as shown in *Figure 8*. Activation of an internal interrupt condition causes a corresponding register bit to be set, *Figure 9*. Each internal interrupt may be individually masked out through the Interrupt Mask register which has the same bit assignments as the Interrupt register and can be loaded from the accumulator. A zero in the Interrupt Mask register inhibits the interrupt and a one enables it. Further interrupt processing is as shown. To determine which of the eight internal conditions caused the interrupt the CPU must read the Interrupt register into the accumulator. To acknowledge receipt of the interrupt certain bits are automatically cleared on a read while others are reset upon service of the particular interrupt.

The conditions under which each of the interrupts are generated and cleared are as follows:

Note: The interrupt flags indicated by an asterisk (\*) are cleared when the Interrupt Register is read.

#### FIGURE 8. Internal Interrupt Register

#### Bit

0 Vertical Interrupt—Generates an interrupt at the end of the display row designated by the Vertical Interrupt Register. Interrupt bit cleared on a CPU read of the interrupt register. If VIR > Vertical Length Register no interrupt will be generated.

FIGURE 9. Internal Interrupt Processing

## Bit

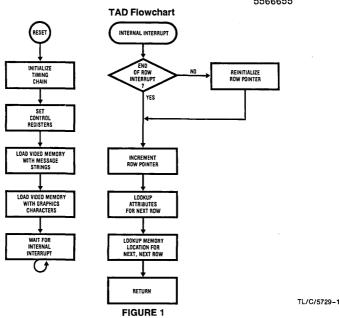

- 1 End of Row Interrupt—Generates an interrupt at the end of each display row when the Current Row Start Register is updated for the next row. Used in conjunction with the Row Sequencing Control Bit (5) in the System Control Register to implement Row Pointer Look-Up Tables and Horizontally Split Screens. Interrupt bit cleared on a CPU write to the Home Register. Does not generate interrupts for those rows blanked during vertical blanking.

- 2 UART Transmit Buffer Empty—Generates an interrupt when the Transmit Buffer empties out after dumping a character into the Transmit Shift Register. Interrupt bit cleared on a CPU write to the Transmit Buffer.

- 3 Transmitter Empty—Generates an interrupt when BOTH the Transmit Buffer and Transmit Shift Register are empty. The interrupt bit is cleared when the CPU loads the transmit buffer.

- 4 UART Receiver Buffer Full—Generates an interrupt when the Receiver Buffer fills up with a character from the Receive Shift Register. Interrupt bit cleared on a CPU read of the Receiver Buffer.

- 5 Light Pen Interrupt—Generates an interrupt on each falling edge detected on the shared LP/RE9 pin. Since only falling edges generate interrupts and the input is sampled each CPU Cycle, a high level must be sampled between falling edges in order to be considered a new interrupt. This interrupt is used to latch the light pen position registers. For further information see Light Pen Description. Interrupt bit cleared on a CPU read of the interrupt register.

#### Bit

- 6 Timer Interrupt—Generates an interrupt when the internal 8-bit Timer overflows from FF to 00. Interrupt bit cleared on a CPU read of the interrupt register.

- 7 Real-Time Interrupt—Generates interrupts at a software programmable frequency that is generally in the Hertz range. (See CPU Clock Generation.) Thus permitting the implementation of a real-time clock or timer. Interrupt bit cleared on a CPU read of the interrupt register.

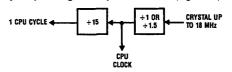

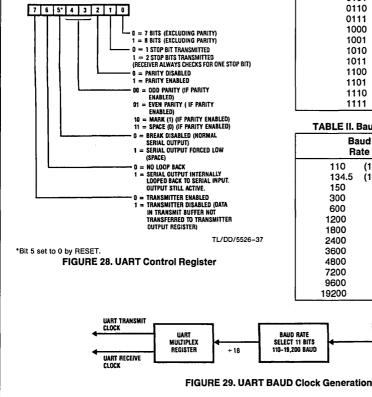

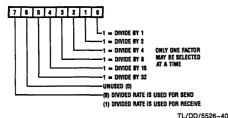

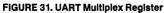

#### 2.1.9 Clock Generation

All chip clocks are derived from the one external crystal connected between pins 22 and 23. This master clock also doubles as the video dot clock. The crystal frequency is constrained to lie within the range of 3 to 18 MHz. The CPU clock is derived from the crystal clock by either using it directly or by dividing down by a factor of 1.5 (*Figure 10*).

TL/DD/5526-17

#### FIGURE 10. CPU Clock Generation

The choice is software programmable through bit 0 in the System Control Register. The exact selection is made in consideration of the fact that the CPU clock must lie within the range of 3 to 12 MHz. In addition, the choice of divide by modes will also impact the display character cell width due to the nature of the video controller. Specifically with  $\div$  1.5

7

the cell width must be  $\geq$  8 dots wide whereas with  $\div$  1 the cell width must be  $\geq$  6 dots wide.

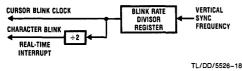

The low clock rates necessary to implement Cursor Blinking, Character Blinking and the Real-Time Interrupt are derived by passing the vertical sync frequency through a 5-bit Blink Rate Divisor Register, *(Figure 11)*. The resultant frequency is used as the Cursor Blink Clock. This clock is then further divided by 2 to yield the Character Blink and Real-Time Interrupt Clocks. For example, to get a 1 Hz real time interrupt, with a 60 Hz system, set the 5 bit Divisor Register to 30 in order to yield a 2 Hz signal which is then divided by 2.

FIGURE 11. Blink Clock Generation

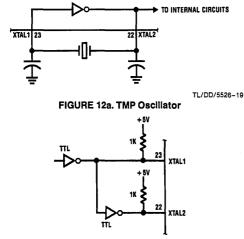

## 2.1.10 Oscillator Operation

The on-board oscillator circuit consists of a phase inverter which, when used with an external parallel resonant tank, (*Figure 12a*), will yield the required oscillator clock. Crystals should be specified for AT cut and parallel resonant operation with the desired load capacitance (typically 20 pF). If one desires to externally generate the clock and input it to the chip, he may do so by driving XTAL1 (pin 23) and XTAL2 (pin 22) as shown in *Figure 12b*.

TL/DD/5526-20

Note: Use AS TTL devices if faster than 12 MHz. FIGURE 12b. External Oscillator Mode

#### 2.2 DISPLAY MEMORY CONTROLLER

The video display data resides in the external Video Memory which is managed by the Display Memory Controller (DMC) through the System Bus. Either the CPU or the Video Controller may access the display memory by presenting its requests to the DMC. A maximum of three Video Memory accesses (Reads or Writes) can be performed by the DMC during each CPU instruction execution cycle. Because the CPU can access the Video Memory, one may expand CPU I/O or data memory by memory mapping into the Video Memory space. Up to 64k locations may be addressed over the 16-bit System Bus. Data word widths may be 8 or 16 bits depending upon whether external character attribute selection is used. The actual bus multiplexing mode is controlled by bit 4 in the System Control register. The Video Controller has the highest priority in obtaining Video Memory accesses with the CPU getting in on a space available basis. If all memory accesses are being taken by the Video Controller (rarely), the CPU is put into a wait state should it try to access video memory. To ease accessing requirements and boost throughput the Video Controller utilizes a 4-level data FIFO which is normally kept full of display data.

#### 2.2.1 Display Memory Control Registers

In order to facilitate the management of video data for such features as a Screen scroll, memory paging and row lookup the DMC utilizes a number of registers which address the video RAM space. Each of these pointers is 16 bits wide and writable or readable from the 16-bit HACC/ACC pair as the case may be. There are 2 video data accessing modes as determined by bit 5 in the SCR, Sequential and Table Lookup. The functions of the pointer registers vary depending upon the accessing mode selected. Their designators are:

- HOME = Home address register. Read and write.

- BEGD = Beginning of diplay RAM. Write only.

- ENDD = End of display RAM. Write only.

- CURS = Cursor address register. Read, Write, Increment, Decrement.

- SROW = Status section register. Write only.

- CRSR = Current row start register. Not directly accessed.

#### 2.2.2 Sequential Access Mode

In this mode display data is accessed from sequential address locations in the video memory until the data requirements for the current screen field are fulfilled. The location from which the first display character is taken is the one pointed to by the HOME register. By modifying the contents of HOME one may implement a row scroll or paging operation. The BEGD and ENDD are used to control the wraparound condition when HOME gets near the end of available display RAM as determined by ENDD. In this instance, when sequential accessing brings us to the end of memory as pointed to by ENDD, the controller wraps around by jumping back to the beginning of display memory as pointed to by BEGD. The value in ENDD should be the last location in display memory + 1. Also the size of the display memory between BEGD and ENDD (ENDD - BEGD) must be an integral number of display rows. The CURS in both accessing modes merely identifies the current cursor position in display memory so that the cursor characteristics can be inserted into the video at the appropriate character position.

In addition to the display of normal video data one may elect to have a special status section displayed using data from a separate section of video memory. The status section would consist of an integral number of display rows on the bottom of the screen. This feature operates by reloading the video RAM pointer with the contents of SROW when the desired row position at which to start the status section comes up. The particular row at which the status display starts is defined in the Timing Chain. Once the video RAM pointer is jumped to SROW, data accessing again proceeds sequentially from there until the data requirements for the current field are satisfied.

7-17

7

7-18

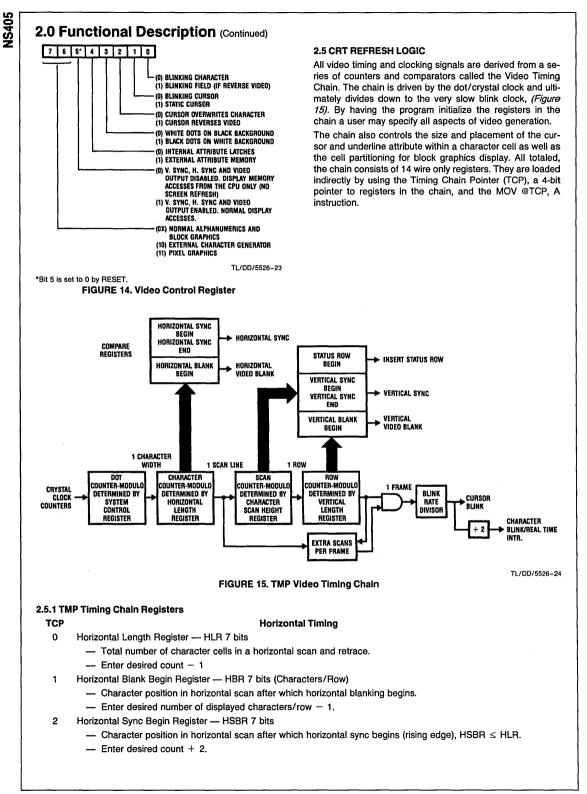

| 2.5.1 TM      | P Timing Chain Registers (Continued)                                                                                                                                                                                                                                              |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCP           | Horizontal Timing                                                                                                                                                                                                                                                                 |

| 3             | Horizontal Sync End Register — HSER 7 bits                                                                                                                                                                                                                                        |

|               | — Character position in horizontal scan after which horizontal sync ends (falling edge), HSER $\leq$ HLR.                                                                                                                                                                         |

|               | Enter desired count + 2.                                                                                                                                                                                                                                                          |

| Note: The     | polarity of the horizontal sync signal can be inverted by switching the values in the two horizontal sync registers.                                                                                                                                                              |

| TCP           | Character Height Definition                                                                                                                                                                                                                                                       |

| 4             | Character Scan Height Register — CSHR 4 bits (see Figure 16a)                                                                                                                                                                                                                     |

| High          | Scan line height of a character cell.                                                                                                                                                                                                                                             |

| Nibble        | - Enter desired number of scan lines - 1.                                                                                                                                                                                                                                         |

| 4<br>Low      | Extra Scans/Frame — ES/F 4 bits<br>— Number of extra scans to be added to a frame if desired.                                                                                                                                                                                     |

| Nibble        | - Enter desired number of extra scans - 1.                                                                                                                                                                                                                                        |

|               | — To get no extra scans make ES/F = CSHR. ES/F must be $\leq$ CSHR.                                                                                                                                                                                                               |

| ТСР           | Vertical Timing                                                                                                                                                                                                                                                                   |

| 5             | Vertical Length Register — VLR 5 bits                                                                                                                                                                                                                                             |

| Ū             | <ul> <li>Total number of display and retrace rows in a frame.</li> </ul>                                                                                                                                                                                                          |

|               | - Enter desired number of rows $-1$ .                                                                                                                                                                                                                                             |

| 6             | Vertical Blank Register — VBR 5 bits (Rows/Screen)                                                                                                                                                                                                                                |

| 0             | <ul> <li>Row position in vertical scan after which vertical blanking begins, VBR &lt; VLR.</li> </ul>                                                                                                                                                                             |

|               | <ul> <li>— How position in vertical scale area which vertical blanking begins, vbH &lt; vEH.</li> <li>— Enter desired number of displayed rows - 1.</li> </ul>                                                                                                                    |

| 7             | Vertical Sync Begin Register — VSBR 4 bits                                                                                                                                                                                                                                        |

| ,<br>High     |                                                                                                                                                                                                                                                                                   |

| Nibble        | <ul> <li>Scan line position in first blank row at which vertical sync begins (falling edge). Sync starts 1 char time after<br/>blanking for that line starts (except when VSBR = CSHR sync will start 1 char time after blanking of the last<br/>displayed scan line).</li> </ul> |

|               | <ul> <li>Enter desired scan line position - 1.</li> </ul>                                                                                                                                                                                                                         |

| 7             | Vertical Sync End Register — VSER 4 bits                                                                                                                                                                                                                                          |

| Low<br>Nibble | <ul> <li>Scan line position after start of vertical sync at which vertical sync ends (rising edge). Sync ends 1 char time after horizontal blanking for that scan line start.</li> </ul>                                                                                          |

|               | <ul> <li>Enter desired scan line position - 1.</li> </ul>                                                                                                                                                                                                                         |

| Note: If VS   | ER = VSBR there will be no vertical sync signal.                                                                                                                                                                                                                                  |

| 8             | Status Row Begin Register — SRBR 5 bits                                                                                                                                                                                                                                           |

|               | <ul> <li>Row count after which the status row is inserted.</li> </ul>                                                                                                                                                                                                             |

|               | <ul> <li>Enter desired row position - 1.</li> </ul>                                                                                                                                                                                                                               |

| TCP           | Cursor and Graphics Control                                                                                                                                                                                                                                                       |

| 9             | Blink Rate 5 bits                                                                                                                                                                                                                                                                 |

| Upper         | <ul> <li>Divider driven by the vertical sync frequency to yield the slow cursor, character and real-time blink rates.</li> </ul>                                                                                                                                                  |

| 5 Bits<br>9   | - Enter desired divisor - 1.                                                                                                                                                                                                                                                      |

| Lower         | Blink Duty Cycle 3 bits<br>— Approximate ON time of blink signal.                                                                                                                                                                                                                 |

| 3 Bits        | - 000 = shortest, 111 = longest (100 = 50% duty cycle).                                                                                                                                                                                                                           |

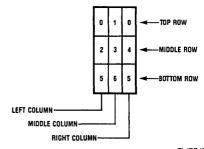

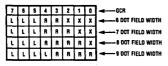

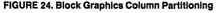

| 10            | Graphics Column Register — GCR 8 bits                                                                                                                                                                                                                                             |

|               | <ul> <li>Assign dot positions to left, middle and right character cell columns for block graphics operation.</li> </ul>                                                                                                                                                           |

| 11            | Graphics Row Register — GRR 8 bits                                                                                                                                                                                                                                                |

|               | <ul> <li>Defines scan count at which middle row for block graphics characters begins (upper nibble) and at which<br/>bottom row begins (lower nibble). The middle row (upper nibble) must be ≥ 1.</li> </ul>                                                                      |

|               | — Enter desired scan count – 1.                                                                                                                                                                                                                                                   |

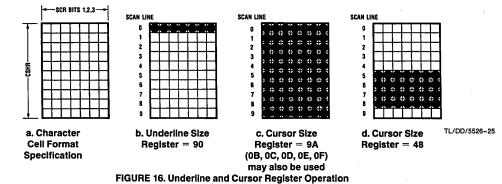

| 12            | Underline Size Register — USR 8 bits (see Figures 16a, b, c)                                                                                                                                                                                                                      |

|               | <ul> <li>Defines the beginning (upper nibble) and ending (lower nibble) scan lines for the underline attribute. Values must be &lt; CSHR.</li> </ul>                                                                                                                              |

| 13            | Cursor Size Register CSR 8 bits (see Figures 16a, b, c)                                                                                                                                                                                                                           |

|               | <ul> <li>Defines the beginning (upper nibble) and ending (lower nibble) scan lines for the cursor. Values must be ≤<br/>CSHR.</li> </ul>                                                                                                                                          |

|               |                                                                                                                                                                                                                                                                                   |

Note: The internal cursor flip-flop gets set to ON whenever a scan line corresponding to the begin cursor nibble is reached, and gets set to cursor OFF whenever a scan line corresponding to the end cursor nibble is reached. The cursor attributes are inserted whenever the character position being displayed corresponds to the one pointed to by the cursor address register. A similar situation applies for characters with the underline attribute selected. Therefore, care should be taken when setting the ES/F register and setting the cursor and underline sizes. In particular the ES/F value should not be between the upper nibble and lower nibble values of the underline size register or between the upper nibble and lower nibble values of the cursor size register. To use the cursor size negister to a value greater than CSHR.

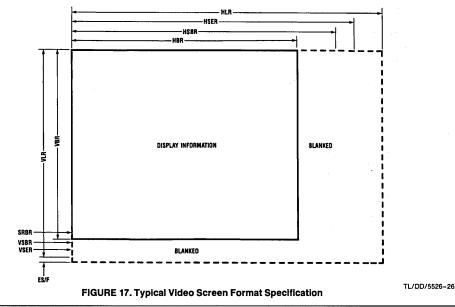

#### 2.5.2 TIMING CHAIN LOAD VALUE EXAMPLE

It is desired to have a display field of 80 columns by 25 rows with the last screen row being a status row. It has been determined that 25 character width times will be necessary to complete horizontal retrace and that Horizontal sync should be positioned to start a full seven character times after blanking and end twenty characters after blanking to give us a total sync width of 13 character times. (See *Figure 17* for example.)

Additionally, vertical retrace will take 23 scan line times to complete with vertical sync starting three scan line times after vertical blanking begins and occupying a total period of 11 scan lines.

It is desired to make the character cells 12 scan lines tall. The cursor will be a block shape and occupy the bottom 11 scan lines in a cell. The underline attribute will actually be a strike through dash occupying the 4th scan line from the top in a cell.

Our line width is 80 displayed characters plus 25 for retrace making HLR = 80 + 25 - 1 = 104. Blanking will start after the 80th character so HBR = 80 - 1 = 79. To achieve seven character times after horizontal blanking, HSBR = 87 + 2 = 89. To achieve twenty character times after blanking HSER = 100 + 2 = 102 (note 102 - 89 = 13 total). Cell height is 12 lines so CSHR = 12 - 1 = 11. Since there are 12 scan lines per cell or row, vertical retrace will require 23/12 = 1 row and 11 scan lines. This makes our total row count VLR = 25 + 1 - 1 = 25 and ES/F = 11 - 1 = 10. Thus, timing chain location 4 would be coded: 1011 1010. We will display 25 rows so VBR = 25 - 1 = 24. Vertical sync will start at the beginning of the fourth scan

line of the row after blanking begins so VSBR = 4 - 1 = 3. It will run for 11 scan lines or specifically the 4, 5, 6, 7, 8, 9, 10, 11, 12, 1, 2 ending at the beginning of the 3rd so VSER = 3 - 1 = 2. The status row will be after the 24th so SRBR = 24 - 1 = 23. To specify the underline and cursor sizes one must remember that the first scan line is numbered 0. To get our 11 line block cursor we begin after the 0 line and end at the end of the 11 line making CSR = 0000 1011. The underline dash will be USR = 0011 0100. Note that the CSHR determines the scan counter modulo and if a scan compare register value (ES/F, VSBR, VSER, USR, CSR) is never reached, the signal end or begin will never be initiated.

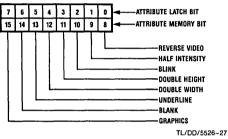

# 2.6 ATTRIBUTES

Eight independent attributes may be inserted it to the video dot stream to affect display characters on either an individual or global basis. The eight attributes along with their con-

FIGURE 18. Attribute Bit Assignments

trol word bit assignments are detailed in *Figure 18*. The scope with which a particular set of attributes affects the display depends upon whether attribute control is internal or external as determined by bit 4 in the VCR.

Attributes are present if the corresponding bit is a ZERO (low).

# 2.6.1 Internal Attribute Selection

In internal mode attribute control comes from one of two internal attribute latches designated AL0 and AL1, either of which is directly loadable from the CPU accumulator. The choice of which of the two is used for a particular display character is determined by bit 7 (MSB) in the display memory data byte with 0 = AL0 and 1 = AL1. (Characters are represented in display memory as ASCII values occupying the low 7 bits of each 8-bit byte thus leaving bit 7 free for attribute control.)

## 2.6.2 External Attribute Selection

In external mode each display character has associated with it, a dedicated attribute field in the form of a high 8-bit extension to the regular display memory character byte. To use this mode the system bus msut be configured for 16-bit bidirectional operation (SCR bit 4 = 1) and external attributes must be selected (VCR bit 4 = 1).

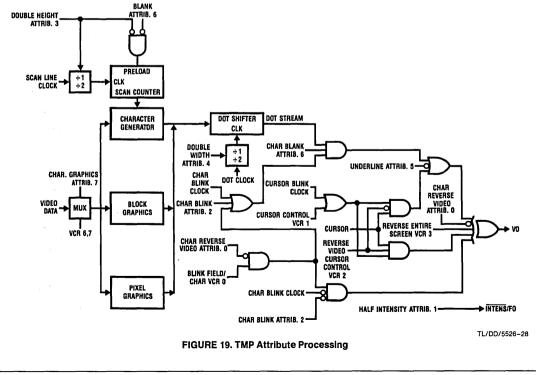

#### 2.6.3 Attribute Processing

Each of the eight attributes may be independently enabled thus yielding a number of possible combinations. The exact processing involved is shown in *Figure 19*. Note that attributes are always present. Whether any of them are active depends upon the particular control bit being enabled in the latch or memory.

7

# 2.6.4 Attribute Operation

Reverse Video: A character and its surrounding cell are reversed in video from what was selected for the rest of the screen.

Half Intensity: To use the half intensity function the shared INTENSITY/FO CLK pin (25) must be selected for INTENSITY operation by setting SCR bit 6 low. In operation the half intensity pin will be low whenever a character for which the attribute is active is being displayed. To perform the actual attenuation function external circuitry must be connected between the INTEN and Video Output pins. In fact the signal may be used for another purpose such as switching between two colors.

Blink: A character or the field around it blinks as selected by VCR bit 0.

- Double Height: A designated character is stretched out so that it will occupy a 2-row tall space. This attribute is implemented by slowing down by half the scan line stepping to the internal character generator. To use this attribute the desired double high character must be placed into the two display memory locations corresponding to the top and bottom row positions. For both locations the double high attribute is set. In addition the Blank attribute for the bottom character is also set to tell the controller it is the bottom half of a double high character. The double high attribute has no effect on element graphics or on pixel graphics displays. If an external character generator is used special circuitry must be employed to implement double high characters.

- Double Width: A designated character is stretched out so that it will occupy a 2-character cell wide space. This attribute is implemented by slowing down by half the clock to the video dot shifter. To use this attribute the desired double wide character must be placed in the left character position and the double wide attribute bit set. The following character position (right) can have any character as it will be ignored.

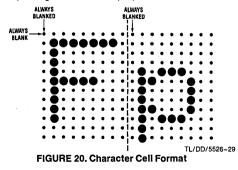

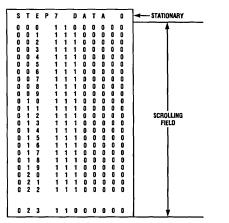

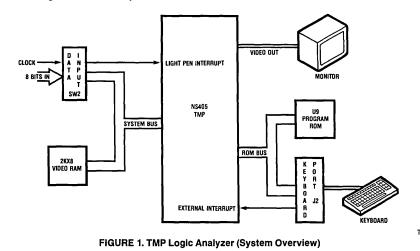

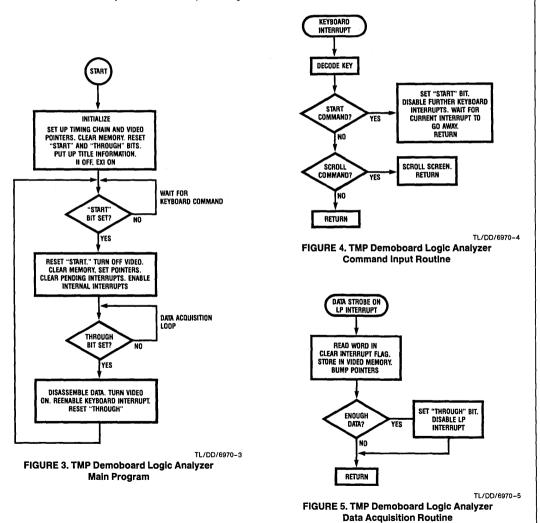

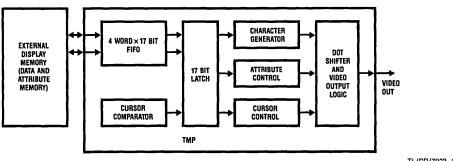

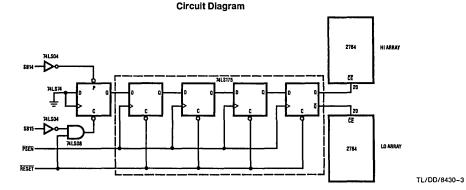

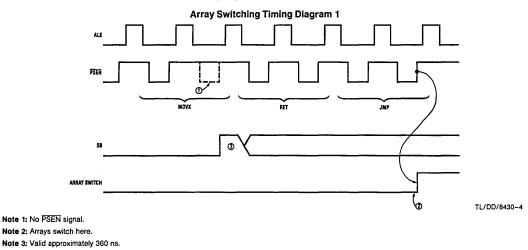

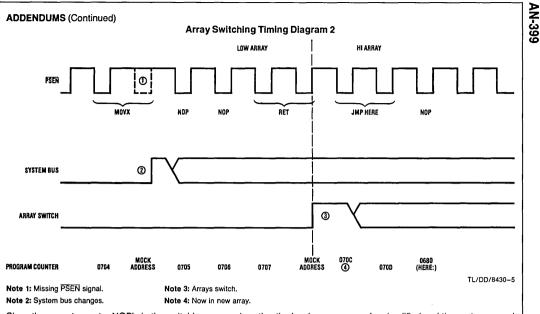

- Underline: If set this attribute causes the underline figure to be added to the video dot stream. Since the underline, like the cursor, can be specified as to position and size in the character cell, the underline can be an overline, block, strike through or any one of a number of effects. The underline overwrites any dot where it overlaps the character.